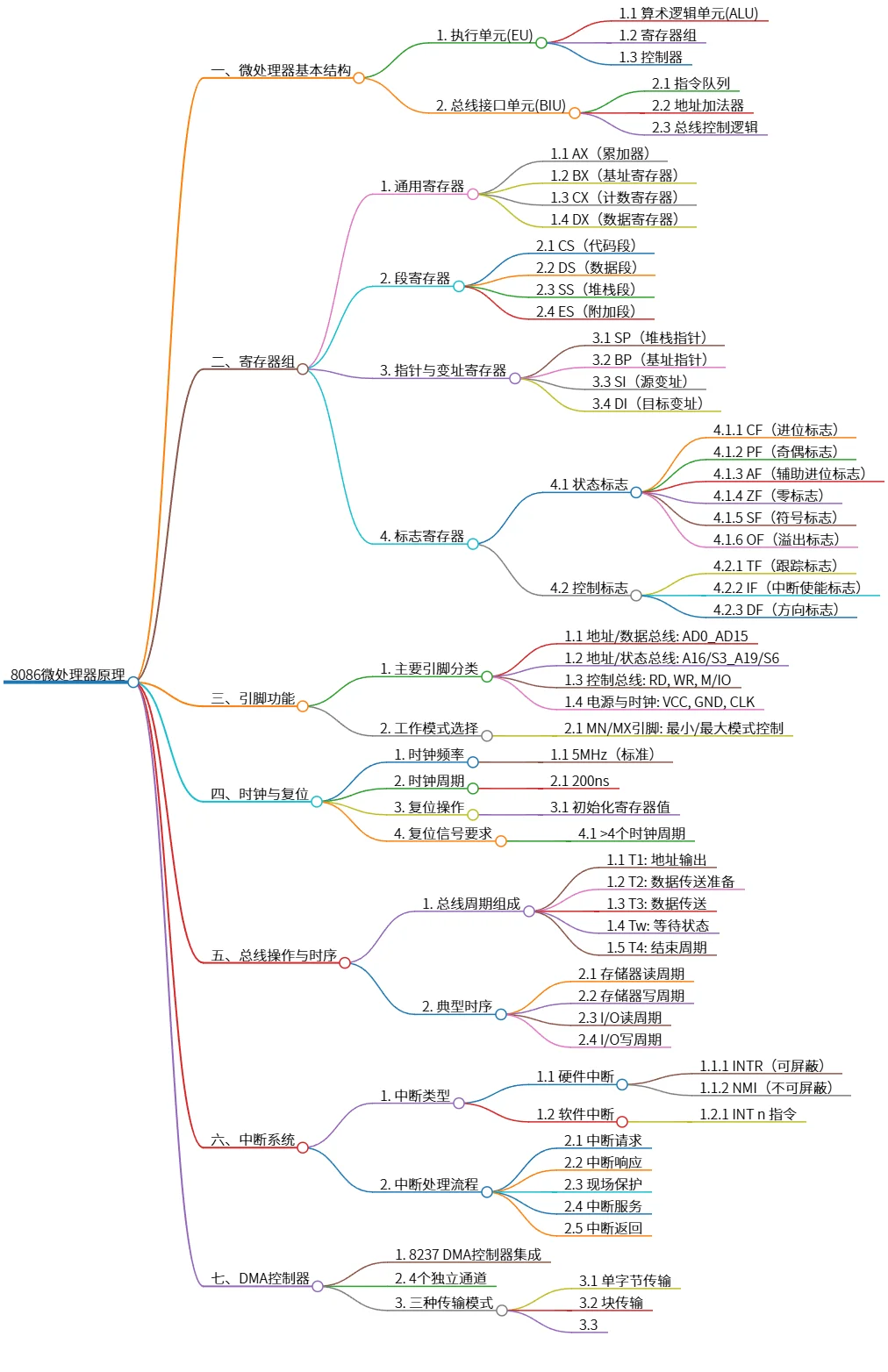

8086微处理器原理与结构、功能及关键技术解析

该思维导图概述了8086微处理器的基本原理,包括微处理器的基本结构(执行单元EU与总线接口单元BIU)、寄存器组、引脚功能、时钟与复位、总线操作与时序、中断系统、DMA控制器、系统组成和关键技术特点。重点介绍了寄存器种类、引脚分类及其功能、总线周期的组成和中断处理流程,以及通过8237 DMA控制器实现的独立通道和传输模式等内容,强调了其兼容性及多处理器系统的支持。

源码

# 8086微处理器原理

## 一、微处理器基本结构

### 1. 执行单元(EU)

#### 1.1 算术逻辑单元(ALU)

#### 1.2 寄存器组

#### 1.3 控制器

### 2. 总线接口单元(BIU)

#### 2.1 指令队列

#### 2.2 地址加法器

#### 2.3 总线控制逻辑

## 二、寄存器组

### 1. 通用寄存器

#### 1.1 AX(累加器)

#### 1.2 BX(基址寄存器)

#### 1.3 CX(计数寄存器)

#### 1.4 DX(数据寄存器)

### 2. 段寄存器

#### 2.1 CS(代码段)

#### 2.2 DS(数据段)

#### 2.3 SS(堆栈段)

#### 2.4 ES(附加段)

### 3. 指针与变址寄存器

#### 3.1 SP(堆栈指针)

#### 3.2 BP(基址指针)

#### 3.3 SI(源变址)

#### 3.4 DI(目标变址)

### 4. 标志寄存器

#### 4.1 状态标志

##### 4.1.1 CF(进位标志)

##### 4.1.2 PF(奇偶标志)

##### 4.1.3 AF(辅助进位标志)

##### 4.1.4 ZF(零标志)

##### 4.1.5 SF(符号标志)

##### 4.1.6 OF(溢出标志)

#### 4.2 控制标志

##### 4.2.1 TF(跟踪标志)

##### 4.2.2 IF(中断使能标志)

##### 4.2.3 DF(方向标志)

## 三、引脚功能

### 1. 主要引脚分类

#### 1.1 地址/数据总线: AD0_AD15

#### 1.2 地址/状态总线: A16/S3_A19/S6

#### 1.3 控制总线: RD, WR, M/IO

#### 1.4 电源与时钟: VCC, GND, CLK

### 2. 工作模式选择

#### 2.1 MN/MX引脚: 最小/最大模式控制

## 四、时钟与复位

### 1. 时钟频率

#### 1.1 5MHz(标准)

### 2. 时钟周期

#### 2.1 200ns

### 3. 复位操作

#### 3.1 初始化寄存器值

### 4. 复位信号要求

#### 4.1 >4个时钟周期

## 五、总线操作与时序

### 1. 总线周期组成

#### 1.1 T1: 地址输出

#### 1.2 T2: 数据传送准备

#### 1.3 T3: 数据传送

#### 1.4 Tw: 等待状态

#### 1.5 T4: 结束周期

### 2. 典型时序

#### 2.1 存储器读周期

#### 2.2 存储器写周期

#### 2.3 I/O读周期

#### 2.4 I/O写周期

## 六、中断系统

### 1. 中断类型

#### 1.1 硬件中断

##### 1.1.1 INTR(可屏蔽)

##### 1.1.2 NMI(不可屏蔽)

#### 1.2 软件中断

##### 1.2.1 INT n 指令

### 2. 中断处理流程

#### 2.1 中断请求

#### 2.2 中断响应

#### 2.3 现场保护

#### 2.4 中断服务

#### 2.5 中断返回

## 七、DMA控制器

### 1. 8237 DMA控制器集成

### 2. 4个独立通道

### 3. 三种传输模式

#### 3.1 单字节传输

#### 3.2 块传输

#### 3.3

图片