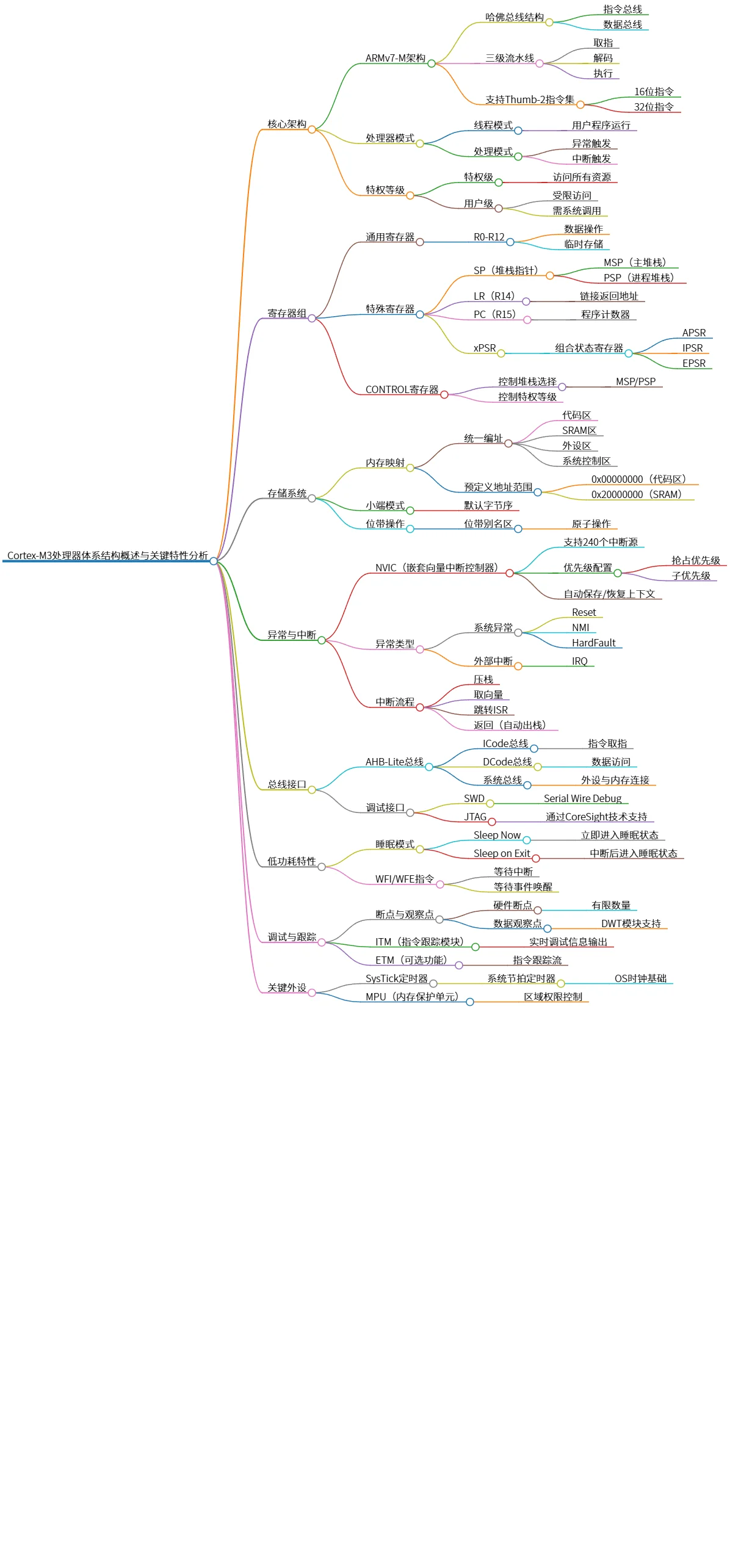

Cortex-M3处理器体系结构概述与关键特性分析

该思维导图概述了Cortex-M3处理器的体系结构,包括核心架构、寄存器组、存储系统、异常与中断、总线接口、低功耗特性、调试与跟踪以及关键外设等内容。处理器基于ARMv7-M架构,采用哈佛结构和三级流水线,支持Thumb-2指令集,具备多种特权等级和线程模式。此外,介绍了NVIC中断控制、AHB-Lite总线接口、低功耗模式及调试功能,为开发嵌入式系统提供基础支持。

源码

# Cortex-M3处理器体系结构概述与关键特性分析

- 核心架构

- ARMv7-M架构

- 哈佛总线结构

- 指令总线

- 数据总线

- 三级流水线

- 取指

- 解码

- 执行

- 支持Thumb-2指令集

- 16位指令

- 32位指令

- 处理器模式

- 线程模式

- 用户程序运行

- 处理模式

- 异常触发

- 中断触发

- 特权等级

- 特权级

- 访问所有资源

- 用户级

- 受限访问

- 需系统调用

- 寄存器组

- 通用寄存器

- R0-R12

- 数据操作

- 临时存储

- 特殊寄存器

- SP(堆栈指针)

- MSP(主堆栈)

- PSP(进程堆栈)

- LR(R14)

- 链接返回地址

- PC(R15)

- 程序计数器

- xPSR

- 组合状态寄存器

- APSR

- IPSR

- EPSR

- CONTROL寄存器

- 控制堆栈选择

- MSP/PSP

- 控制特权等级

- 存储系统

- 内存映射

- 统一编址

- 代码区

- SRAM区

- 外设区

- 系统控制区

- 预定义地址范围

- 0x00000000(代码区)

- 0x20000000(SRAM)

- 小端模式

- 默认字节序

- 位带操作

- 位带别名区

- 原子操作

- 异常与中断

- NVIC(嵌套向量中断控制器)

- 支持240个中断源

- 优先级配置

- 抢占优先级

- 子优先级

- 自动保存/恢复上下文

- 异常类型

- 系统异常

- Reset

- NMI

- HardFault

- 外部中断

- IRQ

- 中断流程

- 压栈

- 取向量

- 跳转ISR

- 返回(自动出栈)

- 总线接口

- AHB-Lite总线

- ICode总线

- 指令取指

- DCode总线

- 数据访问

- 系统总线

- 外设与内存连接

- 调试接口

- SWD

- Serial Wire Debug

- JTAG

- 通过CoreSight技术支持

- 低功耗特性

- 睡眠模式

- Sleep Now

- 立即进入睡眠状态

- Sleep on Exit

- 中断后进入睡眠状态

- WFI/WFE指令

- 等待中断

- 等待事件唤醒

- 调试与跟踪

- 断点与观察点

- 硬件断点

- 有限数量

- 数据观察点

- DWT模块支持

- ITM(指令跟踪模块)

- 实时调试信息输出

- ETM(可选功能)

- 指令跟踪流

- 关键外设

- SysTick定时器

- 系统节拍定时器

- OS时钟基础

- MPU(内存保护单元)

- 区域权限控制

图片